# ZETTLER DISPLAYS

## SPECIFICATIONS FOR LIQUID CRYSTAL DISPLAY

|                      | CUSTOMER APP                | ROVAL           |            |

|----------------------|-----------------------------|-----------------|------------|

|                      |                             |                 |            |

|                      |                             |                 |            |

|                      |                             |                 |            |

|                      |                             |                 |            |

|                      |                             |                 |            |

|                      |                             |                 |            |

|                      |                             |                 |            |

| <b>※ PART</b>        | 'NO.: <u>ATM0350B47B</u> (2 | ZETTLER DISP    | LAYS) V1.1 |

| APPROVAL             |                             | COMPANY<br>CHOP |            |

| CUSTOMER<br>COMMENTS |                             |                 |            |

| COMMENTS             |                             |                 |            |

| ZETTLER DISPLAYS ENGINEERING APPROVAL |            |             |  |  |  |

|---------------------------------------|------------|-------------|--|--|--|

| DESIGNED BY                           | CHECKED BY | APPROVED BY |  |  |  |

| ZZK                                   |            |             |  |  |  |

## **REVISION RECORD**

| REVISION | REVISION DATE | PAGE | CONTENTS          |

|----------|---------------|------|-------------------|

| VER1.0   | 2021-08-25    |      | FIRST ISSUE       |

| VER1.1   | 2024-12-31    | 19   | UPDATE PRECAUTION |

|          |               |      |                   |

|          |               |      |                   |

|          |               |      |                   |

|          |               |      |                   |

|          |               |      |                   |

|          |               |      |                   |

|          |               |      |                   |

|          |               |      |                   |

|          |               |      |                   |

|          |               |      |                   |

|          |               |      |                   |

|          |               |      |                   |

|          |               |      |                   |

|          |               |      |                   |

|          |               |      |                   |

|          |               |      |                   |

|          |               |      |                   |

|          |               |      |                   |

|          |               |      |                   |

|          |               |      |                   |

|          |               |      |                   |

|          |               |      |                   |

|          |               |      |                   |

|          |               |      |                   |

|          |               |      |                   |

#### **\*** CONTENTS

- 1. GENERAL SPECIFICATIONS

- 2. PIN ASSIGNMENT

- 3. OPERATING SPECIFICATIONS

- 4. OPTICAL SPECIFICATIONS

- 5. RELIABILITY TEST

- 6. PRECAUTION FOR USING LCM

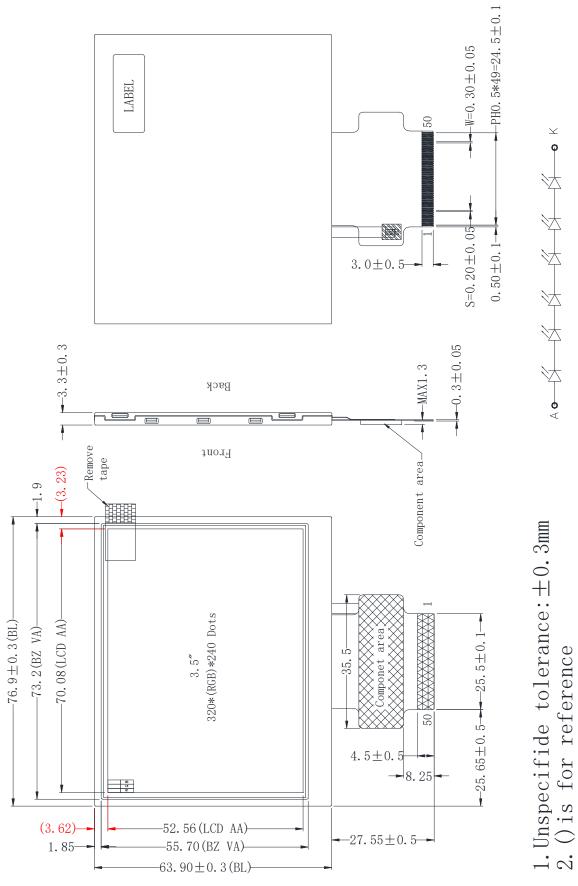

- 7. MECHANICAL DRAWING

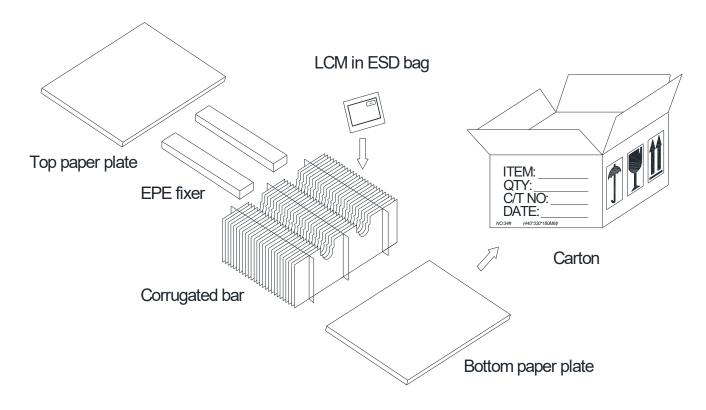

- 8. PACKAGE DRAWING

- 9. INSPECTION SPECIFICATION

## 1. GENERAL SPECIFICATIONS

| Item                            | Specification                    | Remark |

|---------------------------------|----------------------------------|--------|

| 1. LCD size                     | 3.5 inch(Diagonal)               |        |

| 2. Driver element               | a-Si TFT active matrix           |        |

| 3. Resolution                   | 320x(RGB)x240                    |        |

| 4. Display mode                 | Normally white, TN,Transmissive  |        |

| 5. Dot Pitch (W*H)              | 0.073mm(W) x 0.219mm(H)          |        |

| 6. Pixel pitch(W*H)             | 0.219mm(W) x 0.219mm(H)          |        |

| 7. Active Area(W*H)             | 70.08mm(W) x 52.56mm(H)          |        |

| 8. Module size (W*H)            | 76.9mm(W) x 63.9mm(H) x 3.3mm(D) | Note 1 |

| 9. Surface treatment            | Anti-glare                       |        |

| 10. Color arrangement           | RGB-stripe                       |        |

| 11. Color                       | 262K                             |        |

| 12. Viewing angle (L/R/T/B)     | 60/60/60/30                      |        |

| 13. Interface                   | MCU/RGB                          |        |

| 14. LCD controller              | SSD2119AM1                       |        |

| 15. LCM brightness              | 400 cd/m2 Typ.                   |        |

| 16. Backlight driving condition | 20mA @18.6V                      |        |

| 17. Touch panel                 | N.A.                             |        |

| 18. Touch controller            | N.A.                             |        |

| 19. Operation temperature       | -20~70 °C                        |        |

| 20. Weight                      | 32g                              |        |

| 21. RoHS                        | RoHS compliant                   |        |

Note 1: Please refer to mechanical drawing.

## 2. PIN ASSIGNMENT

**TFT LCD Panel Driving Section**FPC Connector is used for the module electronics interface. The recommended model is FH12A-50S-0.5SH manufactured by Hirose.

| Pin No. | Symbol     | Function                                                                             | Level        | Note |

|---------|------------|--------------------------------------------------------------------------------------|--------------|------|

| 1       | VCI        | Booster input voltage pin                                                            | Р            |      |

| 2       | VCI        | Booster input voltage pin                                                            | Р            |      |

| 3       | VSS        | Ground (0V)                                                                          | Р            |      |

| 4       | VDDIO      | Voltage input pin for logic                                                          | Р            |      |

| 5       | VSS        | Ground (0V)                                                                          | Р            |      |

| 6       | RESET      | Reset Signal pin ("Low" is enable)                                                   | I            |      |

| 7       | DC/SDC(RS) | Data or Command select PIN.                                                          | I            |      |

|         |            | 6800 system: E(enable signal)                                                        |              |      |

| 8       | E/RD       | 8080 system: RD(read strobe signal)                                                  | 1            |      |

|         | 2,11,3     | Serial mode: Not use and should be connected to $V_{\text{DDIO}}$ or $V_{\text{SS}}$ | ·            |      |

|         |            | 6800 system: RW (indicates read cycle when high,                                     |              |      |

| 9       | WR         | write cycle when low)                                                                | I            |      |

| 40      | 00         | 8080 system: WR (write strobe signal)                                                | <del> </del> |      |

| 10      | CS         | Chip select                                                                          | l l          |      |

| 11      | SCL        | Serial Clock.                                                                        | l            |      |

| 12      | SD0        | Data output pin in serial interface                                                  | 0            |      |

| 13      | SDI        | Data input pin in serial interface                                                   | I            |      |

| 14      | WSYNC(NC)  | Ram write synchronization output. Leave it OPEN when not used.                       | 0            |      |

|         |            | Data bus                                                                             |              |      |

| 45.00   |            | For parallel mode, 8/9/16/18 bit interface.                                          |              |      |

| 15~32   | D17~D0     | Please refer to Section 15 Interface Mapping Section for definition.                 | I/O          |      |

|         |            | Unused pins should connect to V <sub>SS</sub> .                                      |              |      |

| 33      | VSS        | Ground                                                                               | Р            |      |

| 34      | DOTCLK     | Dot-clock signal and oscillator source                                               | I            |      |

| 35      | HSYNC      | Line Synchronization input                                                           |              |      |

| 36      | VSYNC      | Frame/Ram Write Synchronization input                                                | I            |      |

| 37      | DE         | Display enable pin for controller                                                    | I            |      |

| 38      | VSS        | Ground                                                                               | Р            |      |

| 39      | PS0        |                                                                                      | 1            |      |

| 40      | PS1        | Interface coloct DIM                                                                 | I            |      |

| 41      | PS2        | Interface select PIN                                                                 |              |      |

| 42      | PS3        |                                                                                      |              |      |

| 43      | VSS        | Ground                                                                               | Р            |      |

| 44      | NC (XR)    | NC                                                                                   |              |      |

| 45      | NC (YD)    | NC                                                                                   |              |      |

| 46      | NC (XL)    | NC                                                                                   |              |      |

| 47 | NC (YU) | NC                    |   |  |

|----|---------|-----------------------|---|--|

| 48 | VSS     | Ground                | Р |  |

| 49 | LEDK    | Backlight LED Cathode | I |  |

| 50 | LEDA    | Backlight LED Anode.  | I |  |

I: input, O: output, P: Power

| PS3 | PS2 | PS1 | PS0 | Interface Mode                                                                                 |

|-----|-----|-----|-----|------------------------------------------------------------------------------------------------|

| 0   | 0   | 0   | 0   | 16-bit 6800 parallel interface                                                                 |

| 0   | 0   | 0   | 1   | 8-bit 6800 parallel interface                                                                  |

| 0   | 0   | 1   | 0   | 16-bit 8080 parallel interface                                                                 |

| 0   | 0   | 1   | 1   | 8-bit 8080 parallel interface                                                                  |

| 0   | 1   | 0   | 0   | 9-bit generic D[17:9] (262k colour) + 3-wire SPI If<br>65K color, D12 shorts to D17 internally |

| 0   | 1   | 0   | 1   | 16-bit generic (262k colour) + 3-wire SPI                                                      |

| 0   | 1   | 1   | 0   | 18-bit generic (262k colour) + 3-wire SPI                                                      |

| 0   | 1   | 1   | 1   | 6-bit generic D[17:12] (262k colour) + 3-wire SPI                                              |

| 1   | 0   | 0   | 0   | 18-bits 6800 parallel interface                                                                |

| 1   | 0   | 0   | 1   | 9-bits 6800 parallel interface                                                                 |

| 1   | 0   | 1   | 0   | 18-bit 8080 parallel interface                                                                 |

| 1   | 0   | 1   | 1   | 9-bit 8080 parallel interface                                                                  |

| 1   | 1   | 1   | 0   | 3-wire SPI                                                                                     |

| 1   | 1   | 1   | 1   | 4-wire SPI                                                                                     |

## 3. Operating Specification

#### 3.1 ABSOLUTE MAXIMUM RATINGS

| Item                  | Symbol          | Val  | ues  | Unit  | Remark             |  |

|-----------------------|-----------------|------|------|-------|--------------------|--|

| item                  | Symbol          | Min. | Max. | Oilit | Kemark             |  |

| Power Voltage         | $V_{DD}$        | -0.3 | 5.0  | V     |                    |  |

| Operation Temperature | T <sub>OP</sub> | -20  | 70   | °C    |                    |  |

| Storage Temperature   | T <sub>ST</sub> | -30  | 80   | °C    |                    |  |

| LED Reverse Voltage   | V <sub>R</sub>  | -    | 1.2  | V     | Each LED<br>Note 2 |  |

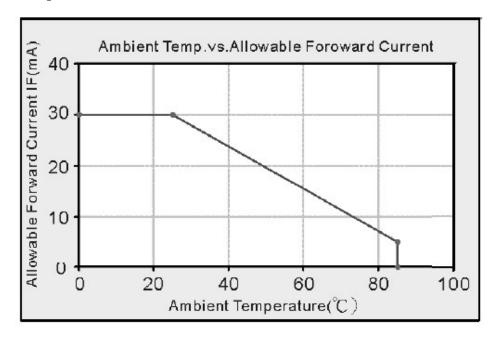

| LED Forward Current   | l <sub>F</sub>  |      | 25   | mA    | Each LED           |  |

**Note 1**: The absolute maximum rating values of this product are not allowed to be exceeded at any times. Should a module be used with any of the absolute maximum ratings exceeded, the characteristics of the module may not be recovered, or in an extreme case, the module may be permanently destroyed.

Note 2: V<sub>R</sub> Conditions: Zener Diode 20mA

#### 3.2 Typical Operation Conditions

| Item                     | Symbol          |        | Values | Unit   | Remark |          |

|--------------------------|-----------------|--------|--------|--------|--------|----------|

| item                     | Syllibol        | Min.   | Тур.   | Max.   | Onit   | Kelliaik |

| Power Voltage            | $V_{DD}$        | 2.5    | 3.3    | 3.6    | V      | Note 1   |

| Input Logic High Voltage | V <sub>IH</sub> | 0.8VCC |        | VCC    | V      |          |

| Input Logic Low Voltage  | $V_{IL}$        | 0      |        | 0.2VCC | V      |          |

**Note 1**: V<sub>DD</sub> setting should match the signals output voltage of customer's system board.

## 3.3 Backlight driving conditions

| Item                      | Symbol |      | Values | Unit | Remark |        |

|---------------------------|--------|------|--------|------|--------|--------|

| item                      | Symbol | Min. | Тур.   | Max. | Oilit  | Kemark |

| Voltage for LED Backlight | $V_L$  | 17.4 | 18.6   | 21.0 | V      | Note 1 |

| Current for LED Backlight | IL     |      | 20     |      | mA     |        |

| LED life time             |        |      | 50000  |      | Н      | Note 2 |

**Note 1**: The LED Supply Voltage is defined by the number of LED at Ta=25 $^{\circ}$ C and I<sub>L</sub> =20mA.

**Note 2**: The "LED life time" is defined as the module brightness decrease to 50% original brightness at Ta=25  $^{\circ}$ C and I<sub>L</sub> =20mA.

## 3.4 Timing Characteristics

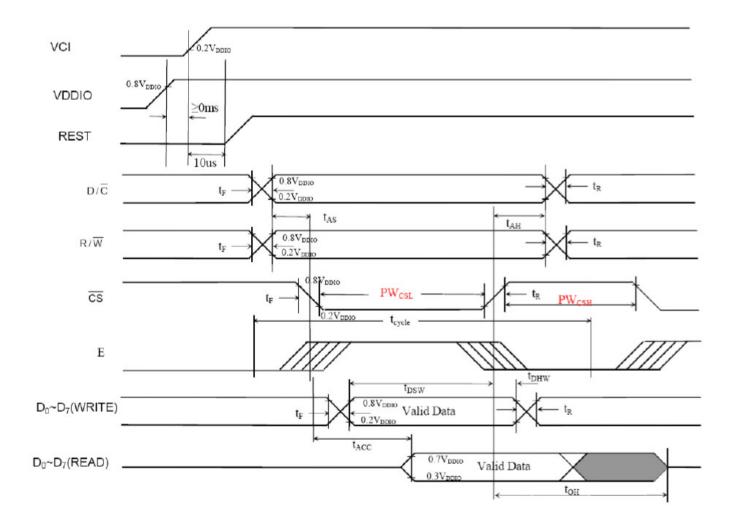

**Table 3-1: Parallel 6800 Timing Characteristics**

$(T_A = -40 \text{ to } 85^{\circ} \text{ C}, V_{DDIO} = 1.4 \text{V to } 2.4)$

| Symbol             | Parameter                                                              | Min  | Тур | Max | Unit |

|--------------------|------------------------------------------------------------------------|------|-----|-----|------|

| t <sub>cycle</sub> | Clock Cycle Time (write cycle)                                         | 75   | -   | -   | ns   |

| t <sub>cycle</sub> | Clock Cycle Time (read cycle) (Based on VOL/VOH = 0.3*VDDIO/0.7*VDDIO) | 1000 | -   | -   | ns   |

| t <sub>AS</sub>    | Address Setup Time (R/W)                                               | 0    | -   | -   | ns   |

| t <sub>AH</sub>    | Address Hold Time (R/W)                                                | 0    | -   | -   | ns   |

| t <sub>DSW</sub>   | Data Setup Time (D0~D7, WRITE)                                         | 5    | -   | -   | ns   |

| t <sub>DHW</sub>   | Data Hold Time (D0~D7, WRITE))                                         | 5    | -   | -   | ns   |

| t <sub>ACC</sub>   | Data Access Time (D0~D7, READ)                                         | 250  | -   | -   | ns   |

| t <sub>OH</sub>    | Output Hold time (D0~D7, READ)                                         | 100  | -   | -   | ns   |

| PWcsl              | Pulse width /CS low (write cycle)                                      | 40   | -   | -   | ns   |

| PW <sub>CSH</sub>  | Pulse width /CS high (write cycle)                                     | 25   | -   | -   | ns   |

| PW <sub>CSL</sub>  | Pulse width /CS low (read cycle)                                       | 500  | -   | -   | ns   |

| PWcsh              | Pulse width /CS high (read cycle)                                      | 500  | -   | -   | ns   |

| t <sub>R</sub>     | Rise time                                                              | -    | -   | 15  | ns   |

| t <sub>F</sub>     | Fall time                                                              | -    | -   | 15  | ns   |

(T<sub>A</sub> = -40 to 85 $^{\circ}$  C, V<sub>DDIO</sub> = 2.4V to 3.6V)

| Symbol             | Parameter                                                              | Min | Тур | Max | Unit |

|--------------------|------------------------------------------------------------------------|-----|-----|-----|------|

| t <sub>cycle</sub> | Clock Cycle Time (write cycle)                                         | 75  | -   | -   | ns   |

| t <sub>cycle</sub> | Clock Cycle Time (read cycle) (Based on VOL/VOH = 0.3*VDDIO/0.7*VDDIO) | 450 | -   | -   | ns   |

| tas                | Address Setup Time (R/W)                                               | 0   | -   | -   | ns   |

| t <sub>AH</sub>    | Address Hold Time $(R/\overline{W})$                                   | 0   | -   | -   | ns   |

| t <sub>DSW</sub>   | Data Setup Time (D0~D7, WRITE)                                         | 5   | -   | -   | ns   |

| t <sub>DHW</sub>   | Data Hold Time (D0~D7, WRITE))                                         | 5   | -   | -   | ns   |

| t <sub>ACC</sub>   | Data Access Time (D0~D7, READ)                                         | 200 | -   | -   | ns   |

| tон                | Output Hold time (D0~D7, READ)                                         | 100 | -   | -   | ns   |

| PWcsl              | Pulse width /CS low (write cycle)                                      | 40  | -   | -   | ns   |

| PW <sub>CSH</sub>  | Pulse width /CS high (write cycle)                                     | 25  | -   | -   | ns   |

| PWcsL              | Pulse width /CS low (read cycle)                                       | 225 | -   | -   | ns   |

| PW <sub>CSH</sub>  | Pulse width /CS high (read cycle)                                      | 225 | -   | -   | ns   |

| t <sub>R</sub>     | Rise time                                                              | -   | -   | 15  | ns   |

| t <sub>F</sub>     | Fall time                                                              | -   | l - | 15  | ns   |

Note: CS can be pulled low during the write cycle, only /WR is needed to be toggled.

Figure 3-1: Parallel 6800-series Interface Timing Characteristics

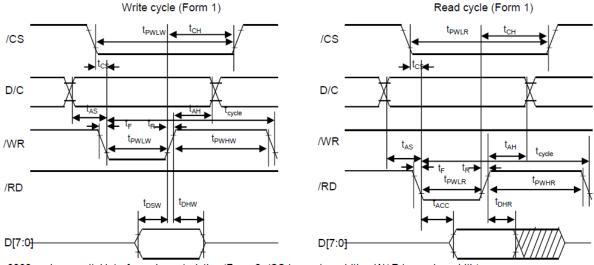

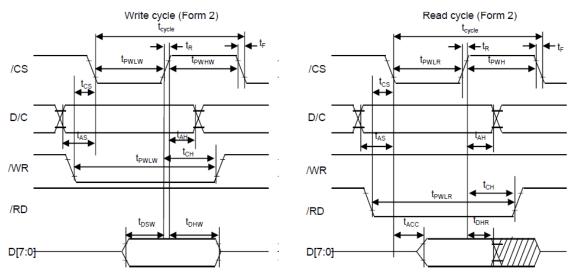

**Table 3-2: Parallel 8080 Timing Characteristics**

| Symbol             | Parameter                                  | Min | Тур | Max | Unit |

|--------------------|--------------------------------------------|-----|-----|-----|------|

| t <sub>cycle</sub> | Clock Cycle Time (write cycle)             | 100 | -   | -   | ns   |

| t <sub>AS</sub>    | Address Setup Time                         | 10  | -   | -   | ns   |

| t <sub>AH</sub>    | Address Hold Time                          | 0   | -   | -   | ns   |

| tcs                | Chip Select Time                           | 0   | -   | -   | ns   |

| t <sub>CH</sub>    | Chip Select Hold Time                      | 0   | -   | -   | ns   |

| t <sub>DSW</sub>   | Write Data Setup Time                      | 10  | -   | -   | ns   |

| t <sub>DHW</sub>   | Write Data Hold Time                       | 10  | -   | -   | ns   |

| t <sub>DHR</sub>   | Read Data Hold Time                        | 100 | -   | -   | ns   |

| t <sub>ACC</sub>   | Access Time (RAM)                          | 250 | -   | -   | ns   |

|                    | Access Time (command)                      |     | -   | -   | ns   |

| t <sub>PWLR</sub>  | Chip Select Low Pulse Width (read RAM)     | 500 | -   | -   | ns   |

| tpwlr              | Chip Select Low Pulse Width (read Command) | 500 | -   | -   | ns   |

| t <sub>PWLW</sub>  | Chip Select Low Pulse Width (write)        | 50  | -   | -   | ns   |

| t <sub>PWHR</sub>  | Chip Select High Pulse Width (read)        | 500 | -   | -   | ns   |

| t <sub>PWHW</sub>  | Chip Select High Pulse Width (write)       | 50  | -   | -   | ns   |

| t <sub>R</sub>     | Rise Time                                  | -   | -   | 15  | ns   |

| t <sub>F</sub>     | Fall Time                                  | -   | -   | 15  | ns   |

Note: All timings are based on 20% to 80% of  $V_{\text{DDIO}}\text{-}V_{\text{SS}}$

#### 8080-series parallel interface characteristics (Form 1: /CS low pulse width > W/ R low pulse width)

8080-series parallel interface characteristics (Form 2: /CS low pulse width < W/ R low pulse width)

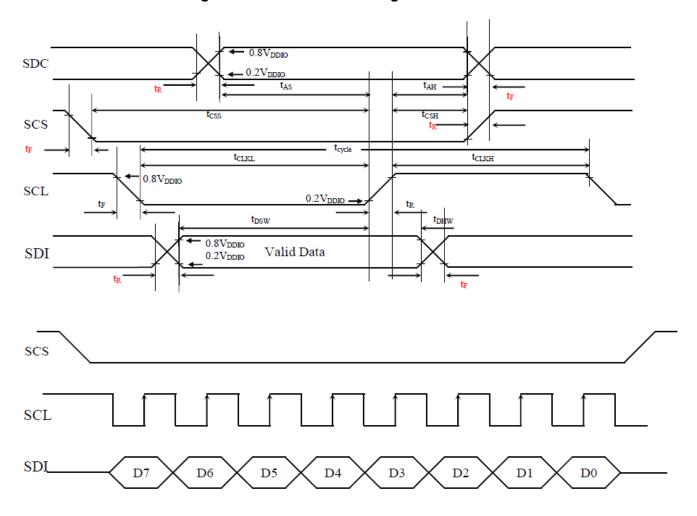

**Table 3-3: Serial Timing Characteristics**

$(T_A = -40 \text{ to } 85^{\circ} \text{ C}, V_{DDIO} = 1.4 \text{V to } 3.6 \text{V})$

| Symbol             | Parameter                                               | Min | Тур | Max | Unit |

|--------------------|---------------------------------------------------------|-----|-----|-----|------|

| t <sub>cycle</sub> | Clock Cycle Time                                        | 77  | -   | -   | ns   |

| f <sub>CLK</sub>   | Serial Clock Cycle Time SPI Clock tolerance = +/- 2 ppm | -   | -   | 15  | MHz  |

| t <sub>AS</sub>    | Register select Setup Time                              | 4   | -   | -   | ns   |

| t <sub>AH</sub>    | Register select Hold Time                               | 5   | -   | -   | ns   |

| t <sub>CSS</sub>   | Chip Select Setup Time                                  | 2   | -   | -   | ns   |

| t <sub>CSH</sub>   | Chip Select Hold Time                                   | 10  | -   | -   | ns   |

| t <sub>DSW</sub>   | Write Data Setup Time                                   | 5   | -   | -   | ns   |

| t <sub>OHW</sub>   | Write Data Hold Time                                    | 10  | -   | -   | ns   |

| t <sub>CLKL</sub>  | Clock Low Time                                          | 38  | -   | -   | ns   |

| t <sub>CLKH</sub>  | Clock High Time                                         | 38  | -   | -   | ns   |

| t <sub>R</sub>     | Rise time                                               | -   | -   | 15  | ns   |

| t <sub>F</sub>     | Fall time                                               | -   | -   | 15  | ns   |

Figure 3-2: 4 wire Serial Timing Characteristics

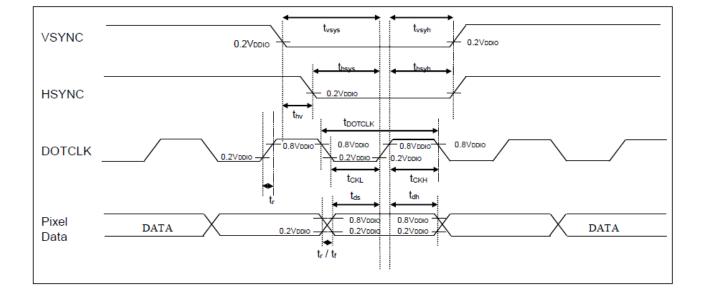

**Table 3-4: RGB Timing Characteristics**

( $T_A$  = -40 to 85° C,  $V_{DDIO}$  = 1.4V to 3.6V )

| Symbol              | Parameter                                    | Min | Тур | Max   | Unit    |

|---------------------|----------------------------------------------|-----|-----|-------|---------|

| f <sub>DOTCLK</sub> | DOTCLK Frequency (70Hz frame rate)           | 1   | 5.5 | 8.2   | MHz     |

| t <sub>DOTCLK</sub> | DOTCLK Period                                | 122 | 182 | 1000  | ns      |

| t <sub>VSYS</sub>   | Vertical Sync Setup Time                     | 20  | -   | -     | ns      |

| t <sub>VSYH</sub>   | Vertical Sync Hold Time                      | 20  | -   | -     | ns      |

| t <sub>HSYS</sub>   | Horizontal Sync Setup Time                   | 20  | -   | -     | ns      |

| t <sub>HSYH</sub>   | Horizontal Sync Hold Time                    | 20  | -   | -     | ns      |

| t <sub>HV</sub>     | Phase difference of Sync Signal Falling Edge | 0   | -   | HFP-1 | tDOTCLK |

| t <sub>CLK</sub>    | DOTCLK Low Period                            | 61  | -   | -     | ns      |

| t <sub>CKH</sub>    | DOTCLK High Period                           | 61  | -   | -     | ns      |

| t <sub>DS</sub>     | Data Setup Time                              | 25  | -   | -     | ns      |

| t <sub>DH</sub>     | Data hold Time                               | 25  | -   | _     | ns      |

Note: External clock source must be provided to DOTCLK pin of SSD2119AM1. The driver will not operate in absence of the clocking signal.

\*HFP: Horizontal Front Porch setting in customers' setup

Figure 3-3: RGB Timing Characteristics

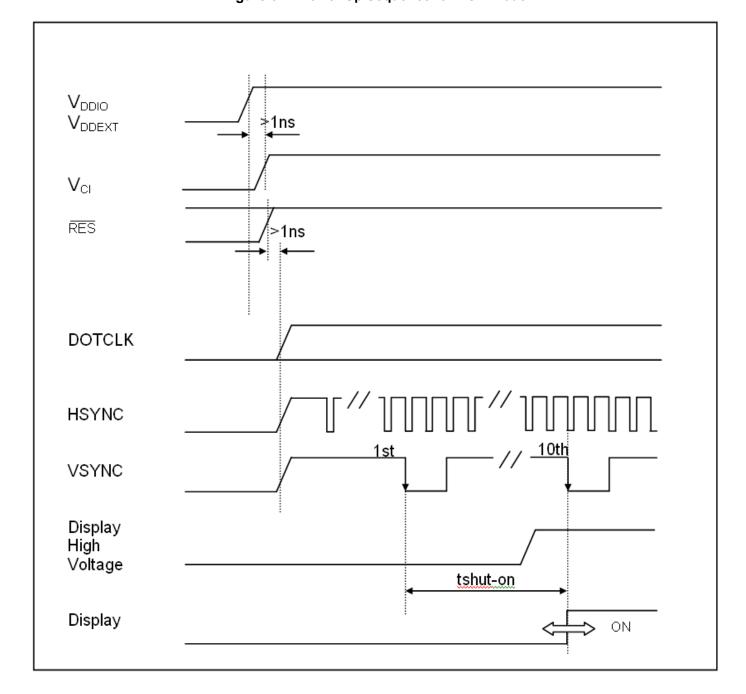

Figure 3-4: Power Up Sequence for RGB mode

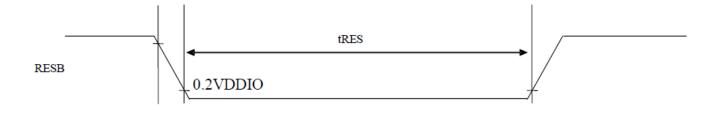

**Table 3-5: Reset Timing**

$(T_A = -40 \text{ to } 85^{\circ} \text{ C}, V_{DDIO} = 1.4 \text{V to } 3.3 \text{V})$

| Symbol           | Parameter            | Min | Тур | Max | Unit |

|------------------|----------------------|-----|-----|-----|------|

| t <sub>RES</sub> | Reset pulse duration | 15  |     |     | us   |

**Figure 3-5: Reset Timing Characteristics**

## **4.0 OPTICAL SPECIFICATIONS**

| ltem                 | Symbol                             | Condition         |      | Values    |      | Unit              | Domork           |  |

|----------------------|------------------------------------|-------------------|------|-----------|------|-------------------|------------------|--|

| item                 | Syllibol                           | Condition         | Min. | Тур. Мах. |      | Oill              | Remark           |  |

|                      | $\theta_{L}$                       | Φ=180°(9 O'CLOCK) | 50   | 60        |      |                   |                  |  |

| Viewing Angle        | $\theta_{R}$                       | Φ=0°(3 O'CLOCK)   | 50   | 60        |      | degree            | Note 1           |  |

| (CR≥10)              | $\theta_{T}$                       | Φ=90°(12 O'CLOCK) | 50   | 60        |      |                   |                  |  |

|                      | $\theta_{B}$                       | Φ=270°(6 O'CLOCK) | 20   | 30        |      |                   |                  |  |

| Response Time        | T <sub>ON +</sub> T <sub>OFF</sub> | DFF               |      | 30        | 50   | msec              | Note 3           |  |

| Contrast Ratio       | CR                                 |                   | 150  | 300       |      |                   | Note 4           |  |

|                      | $W_X$                              | Normal            | 0.26 | 0.31      | 0.36 |                   | Note 2           |  |

| Color Chromaticity   | W <sub>Y</sub>                     | Θ=Φ=0°            | 0.26 | 0.31      | 0.36 |                   | Note 5<br>Note 6 |  |

| Luminance            | L                                  |                   | 350  | 400       |      | cd/m <sup>2</sup> | Note 6           |  |

| Luminance Uniformity | YU                                 |                   | 70   | 80        |      | %                 | Note 7           |  |

#### **Test Conditions:**

- 1. VCC=3.3V, IL=20mA (Backlight current), the ambient temperature is 25  $^{\circ}$ C.

- 2. The test systems refer to Note 2.

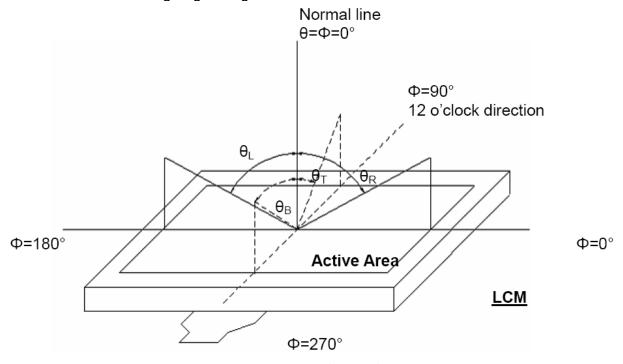

#### Note 1: Definition of viewing angle range

Figure 4.1 Definition of viewing angle.

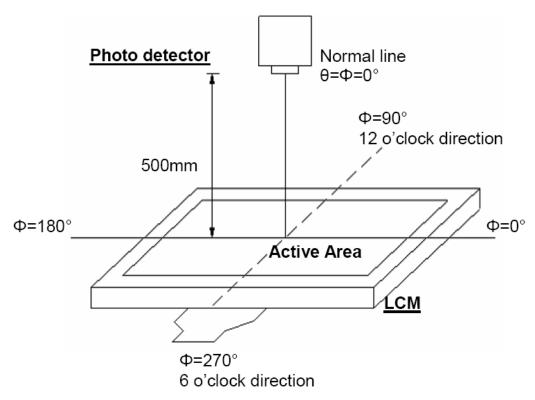

#### Note 2: Definition of optical measurement system.

The optical characteristics should be measured in dark room. After 30 minutes operation, the optical properties are measured at the center point of the LCD screen. (Response time is measured by Photo detector TOPCON

Figure 4.2 Optical measurement system setup

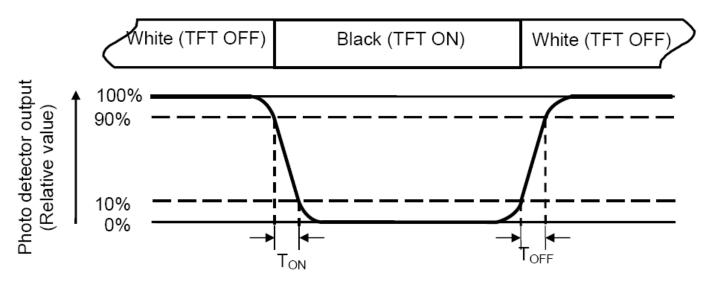

#### Note 3: Definition of Response time

The response time is defined as the LCD optical switching time interval between "White" state and "Black" state. Rise time (TON) is the time between photo detector output intensity changed from 90% to 10%. And fall time (TOFF) is the time between photo detector output intensity changed from 10% to 90%.

Figure 4.3 Definition of response.

#### Note 4: Definition of contrast ratio

Contrast ratio(CR)= Luminance measured when LCD on the "white" state Luminance measured when LCD on the "black" state

#### Note 5: Definition of color chromaticity (CIE1931)

Color coordinates measured at center point of LCD.

**Note 6**: All input terminals LCD panel must be ground while measuring the center area of the panel. The LED driving condition is  $I_L$ =20mA .

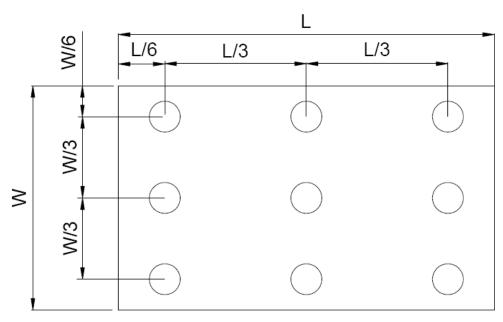

#### Note 7: Definition of Luminance Uniformity

Active area is divided into 9 measuring areas (Refer to Fig. 4-4 ). Every measuring point is placed at the center of each measuring area.

Luminance Uniformity (Yu) =

$$\frac{B_{min}}{B_{max}}$$

L-----Active area length W----- Active area width

Figure 4.3 Definition of measuring points.

Bmax: The measured maximum luminance of all measurement position. Bmin: The measured minimum luminance of all measurement position.

#### **5. RELIABILITY TEST**

| Item                                        | Test Condition Item                                                                                                                          | Remark           |

|---------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| High temperature<br>storage                 | Ta= 80 °C 120hrs                                                                                                                             | Note 1<br>Note 4 |

| Low temperature<br>storage                  | Ta=-30 °C 120hrs                                                                                                                             | Note 1<br>Note 4 |

| High temperature operation                  | Ts= 70 °C 96hrs                                                                                                                              | Note 2<br>Note 4 |

| Low temperature operation                   | Ts=-20 °C 96hrs                                                                                                                              | Note 1<br>Note 4 |

| High temperature/High<br>humidity operation | 90% RH 60°C 120hrs                                                                                                                           | Note 4           |

| Thermal Shock<br>(Non-operation)            | -20 $^{\circ}$ C/30 min $^{\circ}$ +60 $^{\circ}$ C/30 min for a total 30 cycles, Start with cold temperature and end with high temperature. | Note 4           |

| Vibration test                              | Freq:10~55~10Hz Amplitude:1.5mm 2 hours for each direction of X,Y,Z (6 hours for total)                                                      |                  |

| Mechanical shock                            | 60G 6ms,±X, ±Y, ±Z<br>3 times for each direction                                                                                             |                  |

| Package vibration test                      | Random Vibration: 0.015G*G/Hz from 5-200HZ, -6dB/Octave from 200-500HZ 2 hours for each direction of X. Y. Z. (6 hours for total)            |                  |

| Package drop test                           | Height:60 cm<br>1 corner, 3 edges, 6 surfaces                                                                                                |                  |

| Electro static discharge                    | ± 2KV, Human Body Mode, 150pF/330Ω                                                                                                           |                  |

**Note 1**: Ta is the ambient temperature of samples.

**Note 2**: Ts is the temperature of panel's surface.

**Note 3**: In the standard condition, there shall be no practical problem that may affect the display function. After the reliability test, the product only guarantees operation, but don't guarantee all of the cosmetic specification.

**Note 4**: Before cosmetic and function test, the product must have enough recovery time, at least 2 hours at room temperature.

#### 6. PRECAUTION FOR USING LCM

- When design the product with this LCD Module, make sure the viewing angle matches to its purpose of usage.

- 2. As LCD panel is made of glass substrate, dropping the LCD module or banging it against hard objects may cause cracking or fragmentation. Especially at corners and edges.

- Although the polarizer of this LCD Module has the anti-glare coating, always be careful not to scratch its surface.Use of a plastic cover is recommended to protect the surface of polarizer.

- 4. If the LCD module is stored below specified temperature, the LC material may freeze and be deteriorated. If it is stored above specified temperature, the molecular orientation of the LC material may change to Liquid state and it may not revert to its original state. And also excessive temperature and humidity could cause polarizer peel off or bubble. Therefore, the LCD module should always be stored within specified temperature and humidity range. If the LCD modules will be stored for a long time, the recommend temperature/humidity for the storage environment is:

Temperature : 15°C ~ 35°C / Relatively humidity: ≤80%

- 5. Meanwhile please follow other requirements below for storage:

- -Store with no touch on display surface by the anything else. If possible, store the LCD in the packaging situation when it was delivered.

- -If the original package is opened, please store in an anti-static polyethylene bag and seal it so as not to get fresh air outside enter into it.

- LCD modules shall be stored in a dark place. And it shall not be exposed to sunlight nor fluorescent light in storage.

Note: If the storage time is over 1 year, the golden fingers of FPC might be slightly oxidized, but it won't affect the electrical performance, customer can use rubber to clean the golden fingers before assembly or directly assemble the display.

6. Saliva or water droplets must be wiped off immediately as those may leave stains or cause color changes if is remained there for a long time. And water vapor will cause corrosion of ITO electrodes.

If the surface of LCD panel needs to be cleaned, wipe it swiftly with cotton or other soft dry cloth. If it is not still clean enough, blow a breath on the surface and wipe again.

If needed, please just moisten cloth with one of the following solvents:

- Isopropyl alcohol

- Ethyl alcohol

Solvents other than those mentioned above may damage the polarizer. Especially, do not use the following:

- Water

- Ketone

- Aromatic solvents

- 7. The module should be driven according to the specified ratings to avoid malfunction and permanent damage. Applying DC voltage cause a rapid deterioration of LC material. Make sure to apply alternating waveform by continuous application of the M signal. Especially the power ON/OFF sequence should be kept to avoid latch-up of driver LSIs and DC charge up to LCD panel.

- 8. Mechanical Considerations

- a) LCM are assembled and adjusted with a high degree of precision. Avoid excessive shocks and do not make any alterations or modifications. The following should be noted.

- Do not tamper in any way with the tabs on the metal frame.

- Do not modify the PCB by drilling extra holes, changing its outline, moving its components or modifying its pattern.

- 9. Static Electricity

- a) Operator

Wear the electrostatics shielded clothes because human body may be statically charged if not ware shielded clothes. Never touch any of the conductive parts such as the LSI pads; the copper leads on the PCB and the interface terminals with any parts of the human body.

b) Equipment

There is a possibility that the static electricity is charged to the equipment, which has a function of peeling or friction action (ex: conveyer, soldering iron, working table). Earth the equipment through proper resistance (electrostatic earth: 1x10<sup>8</sup> ohm).

Only properly grounded soldering irons should be used.

If an electric screwdriver is used, it should be well grounded and shielded from commutator sparks.

The normal static prevention measures should be observed for work clothes and working benches; for the latter conductive (rubber) mat is recommended.

c) Floor

Floor is the important part to drain static electricity, which is generated by operators or equipment.

There is a possibility that charged static electricity is not properly drained in case of insulating floor. Set the electrostatic earth (electrostatic earth: 1x10<sup>8</sup> ohm).

d) Humidity

Proper humidity helps in reducing the chance of generating electrostatic charges. Humidity should be kept over 50%RH.

e) Transportation/storage

The storage materials also need to be anti-static treated because there is a possibility that the human body or storage materials such as containers may be statically charged by friction or peeling.

The modules should be kept in antistatic bags or other containers resistant to static for storage.

f) Soldering

Soldering anything to this TFT display would void the warranty.

g) Others

The laminator (protective film) is attached on the surface of LCD panel to prevent it from scratches or stains. It should be peeled off slowly using static eliminator.

Static eliminator should also be installed to the workbench to prevent LCD module from static charge.

- 10. Operation

- a) Driving voltage should be kept within specified range; excess voltage shortens display life.

- b) Response time increases with decrease in temperature.

- c) Display may turn black or dark blue at temperatures above its operational range; this is (however not pressing on the viewing area) may cause the segments to appear "fractured".

- d) Mechanical disturbance during operation (such as pressing on the viewing area) may cause the segments to appear "fractured".

- 11. If any fluid leaks out of a damaged glass cell, wash off any human part that comes into contact with soap and water. The toxicity is extremely low but caution should be exercised at all the time.

- 12. Disassembling the LCD module can cause permanent damage and it should be strictly avoided.

- 13. LCD retains the display pattern when it is applied for long time (Image retention). To prevent image retention, do not apply the fixed pattern for a long time. Image retention is not a deterioration of LCD. It will be removed after display pattern is changed.

- 14. Do not use any materials, which emit gas from epoxy resin (hardener for amine) and silicone adhesive agent (dealcohol or deoxym) to prevent discoloration of polarizer due to gas.

- 15. Avoid the exposure of the module to the direct sunlight or strong ultraviolet light for a long time.

## 7. MECHANICAL DRAWING

## **8. PACKAGE DRAWING**

| Carton size         | 53x36x26 | cm  |

|---------------------|----------|-----|

| Quantity per carton | 250      | pcs |

#### 9.0 INSPECTION SPECIFICATION

#### 1. SCOPE SPECIFICATIONS CONTAIN

1.1 DISPLAY QUALITY EVALUATION

1.2 MECHANICS SPECIFICATION

#### 2. SAMPLING PLAN

UNLESS THERE IS OTHER AGREEMENT, THE SAMPLING PLAN FOR INCOMING INSPECTION SHALL FOLLOW MIL-STD-105E.

- 2.1 LOT SIZE: QUANTITY PER SHIPMENT AS ONE LOT (DIFFERENT MODEL AS DIFFERENT LOT ).

- 2.2 SAMPLING TYPE: NORMAL INSPECTION, SINGLE SAMPLING.

- 2.3 SAMPLING LEVEL: LEVEL II.

- 2.4 AQL: ACCEPTABLE QUALITY LEVEL MAJOR DEFECT: AQL=0.65

MINOR DEFECT: AQL=1.0

#### 3. PANEL INSPECTION CONDITION

3.1 ENVIRONMENT:

ROOM TEMPERATURE: 25±5°C.

HUMIDITY: 65±5% RH.

ILLUMINATION: 300 ~ 700 LUX.

3.2 INSPECTION DISTANCE:

35±5 CM

3.3 INSPECTION ANGLE:

THE VISION OF INSPECTOR SHOULD BE PERPENDICULAR TO THE SURFACE OF THE MODULE.

3.4 INSPECTION TIME:

PERCEPTIBILITY TEST TIME: 20 SECONDS MAX.

#### 4. DISPLAY QUALITY

4.1 FUNCTION RELATED:

THE FUNCTION DEFECTS OF LINE DEFECT, ABNORMAL DISPLAY, AND NO DISPLAY ARE CONSIDERED MAJOR DEFECTS.

4.2 BRIGHT/DARK DOTS:

| Defect Type                | Specification | Major | Minor |

|----------------------------|---------------|-------|-------|

| Bright Dots                | N≤ 2          |       | •     |

| Dark Dots                  | N≤ 3          |       | •     |

| Total Bright and Dark Dots | N≤ 4          |       | •     |

Note: 1:

The definition of dot: The size of a defective dot over 1/2 of whole dot is regarded as one defective dot.

Bright dot: Dots appear bright and unchanged in size in which LCD panel is displaying under black pattern.

The bright dot defect must be visible through 2% ND filter

Dark dot: Dots appear dark and unchanged in size in which LCD panel is displaying under pure red, green, blue pattern.

#### 4.3 Pixel Definition:

| R | G | В | R | G | В | R | G | В | Dot Defect          |

|---|---|---|---|---|---|---|---|---|---------------------|

| R | G | В | R | G | В | R | G | В | Adjacent Dot Defect |

| R | G | m | R | G | В | R | G | В | Cluster             |

#### Note 1:

If pixel or partial sub-pixel defects exceed 50% of the affected pixel or sub-pixel area, it shall be considered as1 defect.

#### Note 2:

There should be no distinct non-uniformity visible through 2% ND Filter within 2 sec inspection times.

#### 4.4Visual Inspection specifications:

| Defect 1       | Гуре                                   | Specification Size                                               | Count(N) | Major | Minor |

|----------------|----------------------------------------|------------------------------------------------------------------|----------|-------|-------|

| Dot Shape      |                                        | D ≤0.25 mm                                                       | Ignored  |       |       |

| 1              | cratch and Bubbles in                  | 0.25mm < D ≤ 0.5mm                                               | N ≤ 3    |       |       |

| display area   |                                        |                                                                  |          |       | •     |

| tuopia, ai oa  | ,<br>- D                               | D > 0.5mm                                                        | N=0      |       |       |

|                | -                                      |                                                                  |          |       |       |

| Novden Din     | on (Only for Toyloh monol)             | D≤70mm                                                           | N≤4      |       | _     |

| Newton Rin     | ng (Only for Touch panel)              | D>70mm                                                           | N=0      |       | •     |

| TSD Eich Ev    | os (Only for Touch panel)              | 0.1mm <d≤0.2mm< td=""><td>N≤4</td><td></td><td></td></d≤0.2mm<>  | N≤4      |       |       |

| 1 SP FISH EY   | es (Only for Touch panel)              | 0.2mm <d≤0.3mm< td=""><td>N≤3</td><td></td><td>•</td></d≤0.3mm<> | N≤3      |       | •     |

| (Bubble/Den    | t)                                     | 0.3 <d≤0.4< td=""><td>N≤2</td><td></td><td></td></d≤0.4<>        | N≤2      |       |       |

| Line Shape     |                                        | W ≤ 0.01 mm                                                      | Ignored  |       |       |

| •              | Scratch · Lint and Bubbles             | 0.01mm< W ≤ 0.05mm                                               | N < 2    |       |       |

| in display are |                                        | and L ≤ 3mm                                                      | N ≤ 3    |       | •     |

|                |                                        | W > 0.05mm or L > 3 mm                                           | N=0      |       |       |

|                | L ———————————————————————————————————— |                                                                  |          |       |       |

| Bubble in ce   | ll (active area)                       | It should be found by eyes                                       |          | •     |       |

|                | Scratch                                |                                                                  |          |       | •     |

| Bezel          | Dirt                                   | No harm                                                          |          |       | •     |

|                | Wrap                                   | No harm                                                          |          | •     |       |

|                | Sunken                                 | No harm                                                          |          | •     |       |

|                | No label                               |                                                                  |          |       | •     |

|                | Inverted label                         | No                                                               |          |       | •     |

|                | Broken                                 |                                                                  |          |       | •     |

| 1 -11          | Dirt                                   | Word can be read.                                                |          |       | •     |

| Label          | Not clear                              |                                                                  |          |       | •     |

|                | Word out of shape                      | No                                                               |          |       | •     |

|                | Mistake                                | No                                                               |          |       | •     |

|                | Position                               | Be attached on right position                                    | n        |       | •     |

|                | Not enough                             | No                                                               |          |       | •     |

| Screw          | Limp                                   | No                                                               |          | •     |       |

| <u> </u>       | P                                      | 1                                                                |          | 1     | I .   |

| Connector | Connection status | No bend on pins and damage | • |

|-----------|-------------------|----------------------------|---|

| FPC/FFC   | Broken            | No                         | • |

Note: Extraneous substance and scratch not affecting the display of image, for instance, extraneous substance under polarizer film but outside the display area, or scratch on metal bezel and backlight module or polarizer film outside the display area, shall not be considered as defective or non-conforming.